# **Universal CMOS-Foundry Compatible Platform for Ultra-Low Loss SOI Waveguide Bends**

Kaylx Jang,1,\* Asher Novick,1 Anthony Rizzo,1 and Keren Bergman1

<sup>1</sup>Department of Electrical Engineering, Columbia University, New York, NY, 10027, USA \*kaylx.jang@columbia.edu

**Abstract:** We report a universal, foundry-agnostic, broadband, and ultra low-loss platform for SOI waveguide bends using fully-parameterized, varying-width, hybrid-Euler geometry. We measure record  $R = 1.75 \,\mu m$  IL of  $0.0055 \,dB/180^{\circ}$  at  $1550 \,nm$ . © 2023 The Author(s)

#### 1. Introduction

Next-generation data center and high-performance computing systems require integrated optics that are high-yield, energy-efficient, and compact in order to achieve performance and cost metrics [1]. Complementary metal-oxide-semiconductor (CMOS) fabrication of photonic integrated circuits (PICs) on high-index-contrast silicon-on-insulator (SOI) platforms can address these requirements. Advances in 2.5D and 3D packaging technologies [2] emphasize the importance of maintaining device performance while increasing device density which directly impacts critical metrics such as areal bandwidth density and cost per unit area.

The most ubiquitous photonic device is the waveguide bend—used in everything from routing to constructing complex-compound silicon photonic (SiPh) devices. Densely designed PICs can contain hundreds or thousands of waveguide bends which costs space and several decibels of loss depending on bend performance. Therefore, compact low-loss bends can improve bandwidth density and cost metrics while enabling devices such as ultra-wide FSR microring resonators (MRRs) for dense-wavelength division-multiplexing (DWDM) applications. Previous works have achieved extremely tight bend radii over a given optical bandwidth but require exotic materials, unique processing steps, and/or special design rules not available in all foundries [3–5]. Increasing the center width in simpler hybrid-Euler-like SOI waveguide bends has been shown to improve 90° bend performance [6]. Thus, producing a universal, parameterizable platform for compact and ultra low-loss bends, at any angle, is important for achieving critical system metrics and realizing novel device designs.

This work describes and experimentally demonstrates fully-parameterized, broadband, ultra low-loss, CMOS-compatible bends with a measured insertion loss (IL) of 0.0055 dB/180° for effective bend radius ( $R_{eff}$ ) =  $1.75 \,\mu m$  at 1550 nm across 200 nm of bandwidth in a commercial 300 mm CMOS foundry. This platform allows for arbitrary bend angles and waveguide widths without the inclusion of exotic materials or process steps.

#### 2. Design Principles and Geometric Model

The primary loss mechanisms for waveguide bends are (i) reflections and radiation loss from abrupt modal mismatches between straight and bent sections, (ii) radiation loss from decreased lateral index contrast in the bent section, and (iii) modal interaction with sidewall roughness (SWR). Initial work improved radial bends by using Euler (aka 'clothoid') bends to reduce (i) [4]. Following work reduced (ii) by using a radial section in the center of an Euler bend to reduce maximum curvature (1/R) while maintaining performance, called a hybrid-Euler bend [7].

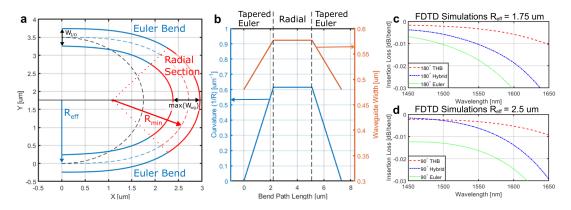

This work proposes further reducing (ii) and (iii) by linearly varying the waveguide width along the curvature (1/R) of the hybrid-Euler bend. The varied-width extends the inner edge of the radial section closer to the bend origin, which we refer to as a tapered-hybrid bend (THB). Fig. 1 illustrates the THB geometry and shows finite-difference time-domain (FDTD) results for the highest performing  $180^{\circ}$  ( $R_{eff} = 1.75 \,\mu\text{m}$ ) and  $90^{\circ}$  ( $R_{eff} = 2.5 \,\mu\text{m}$ ) Euler, hybrid-Euler, and THB at equivalent radii for a 220 nm tall silicon waveguide with 480 nm wide input and output ports. Fig. 1a highlights the Euler and radial sections of a  $180^{\circ}$  THB compared to a normal radial bend. Fig. 1b illustrates how both the curvature and width of a  $180^{\circ}$  THB vary linearly along the tapered Euler sections and then remains constant in the center radial section. Fig. 1c and 1d compare 3D FDTD results for the best performing  $180^{\circ}$  and  $90^{\circ}$  Euler, hybrid-Euler, and THB. At 1550 nm, the IL of a  $180^{\circ}$  THB at  $R_{eff} = 1.75 \,\mu\text{m}$  was 0.00336 dB/bend while the hybrid-Euler was 0.01038 dB/bend. The IL for a  $90^{\circ}$  THB at  $R_{eff} = 2.5 \,\mu\text{m}$  was 0.00329 dB/bend while the hybrid-Euler was 0.00623 dB/bend. The THB showed significantly lower losses per bend compared to the hybrid-Euler bend.

The parameterized geometric model shown in Fig. 1a takes five parameters: the effective bend radius ( $R_{eff}$ ), the bend angle ( $\theta$ ), the hybridization ratio (or the ratio in path length between Euler to radial sections) ( $r_h$ ), the input

Fig. 1. a)  $R_{eff} = 180^{\circ}$  THB geometry made with linearly-tapered input and output Euler sections with a radial section in the middle. b) Linearly varying bend curvature (1/R) [µm<sup>-1</sup>] of Euler sections on either side of a radial section with constant curvature. Simulated comparison of the highest performing Euler, hybrid-Euler, and THB for c)  $R_{eff} = 180^{\circ}$  and d)  $R_{eff} = 90^{\circ}$ .

and output waveguide widths  $(W_{IO})$ , and the waveguide width as it varies over the path length  $(W_{Wg})$ . The complete polygonal geometry is described as follows:

$$S[x] = \int_{0}^{x} \sin(t^{2}) dt, \qquad C[x] = \int_{0}^{x} \cos(t^{2}) dt$$

$$\phi_{min} = 2\theta r_{h} / (1 + 2r_{h}), \qquad \Phi = (\theta - \phi_{min}) / 2, \qquad \theta_{mid} = \theta / 2$$

$$r_{SR} = \frac{S_{mid}}{R_{min}} = 4 \tan^{-1} \left( \sqrt{\tan(\Phi)^{2} + 1} - 1 \right) \cot(\Phi)$$

(3)

$$\phi_{min} = 2\theta r_h / (1 + 2r_h), \qquad \Phi = (\theta - \phi_{min})/2, \qquad \theta_{mid} = \theta/2$$

(2)

$$r_{SR} = \frac{S_{mid}}{R_{min}} = 4 \tan^{-1} \left( \sqrt{\tan(\Phi)^2 + 1} - 1 \right) \cot(\Phi)$$

(3)

$$S_{mid} = R_{eff} \left( \cot \left( \theta_{mid} \right) \left( C \left[ \sqrt{\frac{r_{SR}}{\pi}} \right] \sqrt{\frac{\pi}{r_{SR}}} - \frac{\sin \left( \Phi \right)}{r_{SR}} \right) + S \left[ \sqrt{\frac{r_{SR}}{\pi}} \right] \sqrt{\frac{\pi}{r_{SR}}} + \frac{\cos \left( \Phi \right)}{r_{SR}} \right)^{-1}. \tag{4}$$

Having found  $r_{SR}$  and  $S_{mid}$  allows solving for  $R_{min} = S_{mid}/r_{SR}$ . The  $\{x,y\}$  vertices of the first section of Euler bend,  $\{x_1, y_1\}$ , can then be solved as:

$$\{x_1, y_1\} = \sqrt{R_{min}S_{mid}\pi} \left\{ C \left[ \frac{S}{\sqrt{R_{min}S_{mid}\pi}} \right], \quad S \left[ \frac{S}{\sqrt{R_{min}S_{mid}\pi}} \right] \right\}. \tag{5}$$

Where S is the bend's path length from 0 to  $S_{mid}$ . The vertices for the second half of the bend,  $\{x_2, y_2\}$ , are symmetric to the first half. The axis of rotation,  $\{x_c, y_c\}$ , and resulting reflected and rotated vertices are solved as:

$$\{x_c, y_c\} = \left\{ C \left[ \frac{S_{mid}}{\sqrt{R_{min}S_{mid}\pi}} \right] \sqrt{R_{min}S_{mid}\pi} - R_{min}\sin(\Phi), \quad S \left[ \frac{S_{mid}}{\sqrt{R_{min}S_{mid}\pi}} \right] \sqrt{R_{min}S_{mid}\pi} + R_{min}\cos(\Phi) \right\}$$

$$\{x_2, y_2\} = \left\{ (x_c - x_1)\cos(\theta) + (y_1 - y_c)\sin(-\theta) + x_c, \quad -(x_c - x_1)\sin(-\theta) + (y_1 - y_c)\cos(\theta) + y_c \right\}$$

$$(6)$$

Connecting the two halves of the Euler bend is a radial arc defined by the vertices  $\{x_{rad}, y_{rad}\}$ ,

$$\{x_{rad}, y_{rad}\} = R_{min}\{\cos(\theta_{rad}) + x_c, \quad \sin(\theta_{rad}) + y_c\}$$

(7)

where  $3\pi/2 + \Phi \le \theta_{rad} \le 3\pi/2 + \Phi + \phi_{min}$ . Width is added to the bend path by solving the inner and outer vertices:

$$\theta_{eff} = \theta_{mid} \left( S / S_{mid} \right)^2 \tag{8}$$

Outer Vertices:

$$\{x_{1,o}, y_{1,o}\} = \{x_1 + (W_{IO}/2)\sin(\theta_{eff}), y_1 - (W_{IO}/2)\cos(\theta_{eff})\}$$

Inner Vertices:  $\{x_{1,i}, y_{1,i}\} = \{x_1 - (W_{wg} - W_{IO}/2)\sin(\theta_{eff}), y_1 + (W_{wg} - W_{IO}/2)\cos(\theta_{eff})\}$  (9)

## **Experimental Results and Application in MRR Structure**

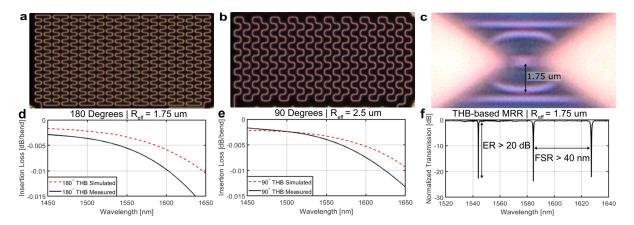

Fig. 2a and 2b show cutback test structures for 180° and 90° THBs both fabricated in a 300 mm CMOS foundry. Fig. 2d and 2e show good agreement between simulated and measured performance for both 180° and 90° THBs. Fig. 2d shows simulated and measured IL of 0.00336 dB and 0.00554 dB, respectively, at 1550 nm for a 180° THB with  $R_{eff} = 1.75 \,\mu\text{m}$ ,  $r_h = 0.65$ , and  $W_{wg,max} = 577 \,\text{nm}$ . Fig. 2e shows simulated and measured IL of 0.00329 dB and 0.00394 dB, respectively, at 1550 nm for a 90° THB with  $R_{eff} = 2.5 \,\mu\text{m}$ ,  $r_h = 0.4$ , and  $W_{wg,max} = 550 \,\text{nm}$ . Additional losses are likely due to sidewall roughness and sidewall angle not accounted for in simulation. Fig. 2c shows a micrograph of an MRR constructed using two 180° THBs, including an integrated heater. Fig. 2f shows measurement results for the constructed MRR.

Fig. 2. Microscope images of **a**) 180° and **b**) 90° THB test structures and (**c**) an MRR using two concatenated 180° THBs. Spectral transmission of a **d**) 180° THB with simulated and measured IL of 0.00336 dB and 0.00554 dB, respectively, **e**) 90° THB with simulated and measured IL of 0.00329 dB and 0.00394 dB, respectively, and **f**) THB-based MRR with symmetric through and drop coupling geometry resulting in critical coupling, implying negligible round trip loss in the MRR [8].

#### 4. Conclusion

We propose a universal platform for broadband, ultra low-loss SOI waveguide bends using a varying-width, hybrid-Euler geometry for meeting next-generation system performance metrics and enabling novel device design, such as low-loss ultra-wide FSR MRRs. This platform has a fully-parameterized geometric model that showed significantly lower simulated and measured IL compared to other bend types for  $180^\circ$  and  $90^\circ$  bends across 200 nm of bandwidth. This platform is foundry-agnostic and does not require exotic processes or materials and complies with most commercial foundry design rules, such as minimum feature size. This universal platform directly supports next-generation PICs requiring ultra-high bandwidth density through more compact routing and novel resonators designs, allowing for an easy transition between published results and product-ready devices.

## References

- A. Rizzo, S. Daudlin, A. Novick et al., "Petabit-scale silicon photonic interconnects with integrated kerr frequency combs," IEEE J. Sel. Top. Quantum Electron. 29, 1–20 (2023).

- 2. S. Daudlin *et al.*, "3d-integrated multichip module transceiver for terabit-scale dwdm interconnects," in *Optical Fiber Communication Conference (OFC) 2021*, (Optica Publishing Group, 2021), p. Th4A.4.

- 3. Y. Qian, S. Kim, J. Song, G. P. Nordin, and J. Jiang, "Compact and low loss silicon-on-insulator rib waveguide 90° bend," Opt. Express 14, 6020–6028 (2006).

- 4. M. Cherchi *et al.*, "Dramatic size reduction of waveguide bends on a micron-scale silicon photonic platform," Opt. Express **21**, 17814–17823 (2013).

- 5. Z. Zhang, Y. Shi, B. Shao, T. Zhou, F. Luo, and Y. Xu, "Design of compact, broadband, and low-loss silicon waveguide bends with radius under 500 nm," Photonics **9** (2022).

- 6. J. H. Song, T. D. Kongnyuy, P. D. Heyn, S. Lardenois, R. Jansen, and X. Rottenberg, "Low-loss waveguide bends by advanced shape for photonic integrated circuits," J. Light. Technol. 38, 3273–3279 (2020).

- 7. T. Fujisawa, S. Makino, T. Sato, and K. Saitoh, "Low-loss, compact, and fabrication-tolerant si-wire 90 waveguide bend using clothoid and normal curves for large scale photonic integrated circuits," Opt. express 25, 9150–9159 (2017).

- 8. W. Bogaerts et al., "Silicon microring resonators," Laser & Photonics Rev. 6, 47–73 (2012).

Acknowledgements: This work was supported in part by the U.S. Defense Advanced Research Projects Agency under PIPES Grant HR00111920014 and in part by the U.S. Advanced Research Projects Agency–Energy under ENLITENED Grant DE-AR000843. The wafer/chip fabrication and custom device processing were provided by AIM Photonics/SUNY Poly Photonics engineering team and fabricator in Albany, New York