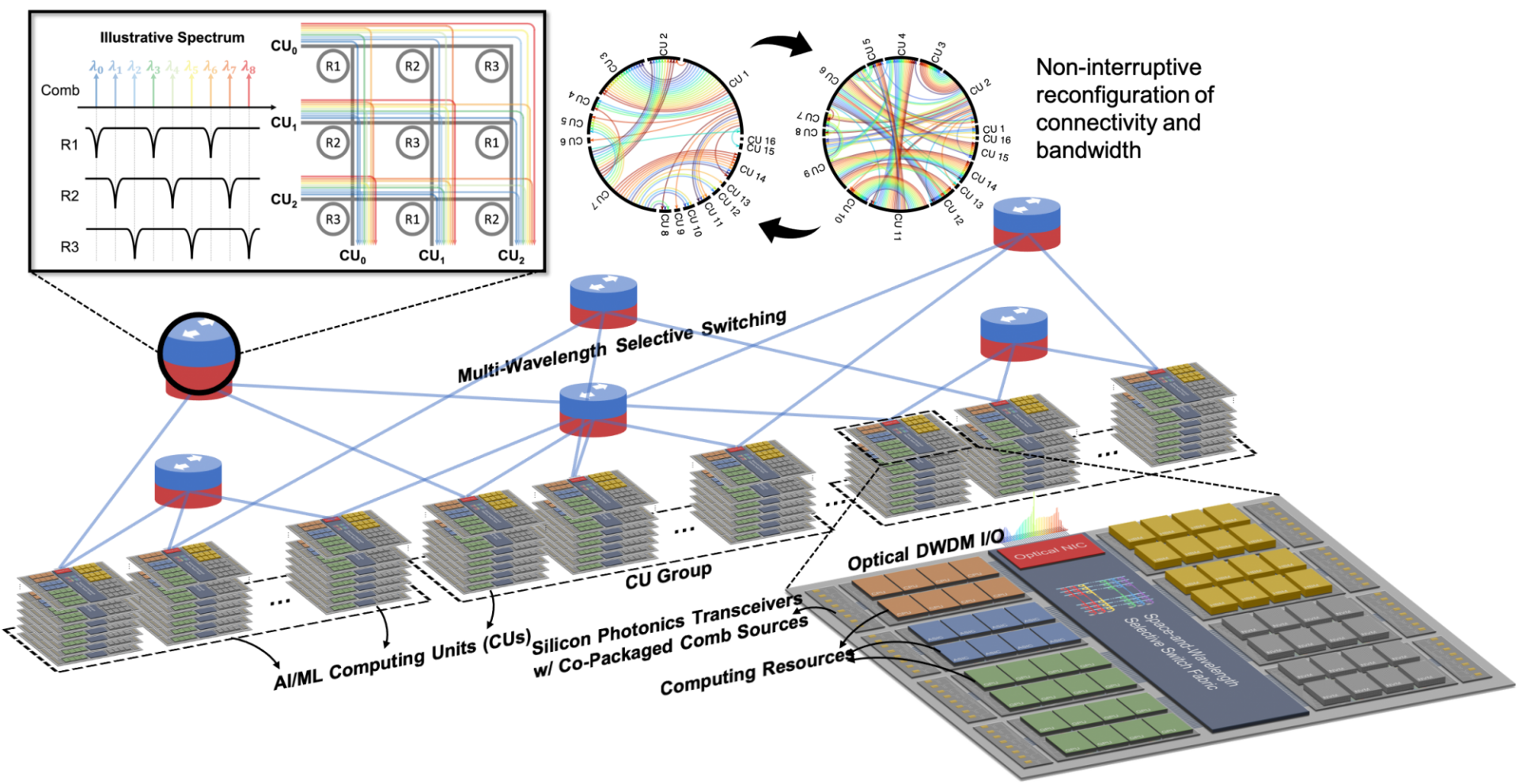

This research area aims to explore the design space of flexible accelerator network architectures by leveraging reconfigurable wavelength selective switches and Dense Wavelength-Division Multiplexing (DWDM) transceivers. The proposed architecture is evaluated using network-level simulations and testbed experiments, and its performance is compared with state-of-the-art accelerator architectures. A key objective of our work to develop a flexible, photonic interconnect that enhances communication efficiency in AI/ML applications.